Useful picture here:

https://www.itjungle.com/2018/03/05/deal-power9-memory-entry-servers/

The P9-Nimbus processor has 8 channels. Sforza pins out 2 per right/left side; the other 2 on each side are unusable.

First factor: does the system mainboard connect 2 DIMMs to the same memory channel or 1 DIMM per memory channel for each of the 4? If 1 per channel, that is best performance and most flexibility, opening the possibility that mismatched DIMM sizes would each be used at full capacity. If 2 DIMMs are connected on one channel, they must be fully matched (size, speed, maybe even manufacturer).

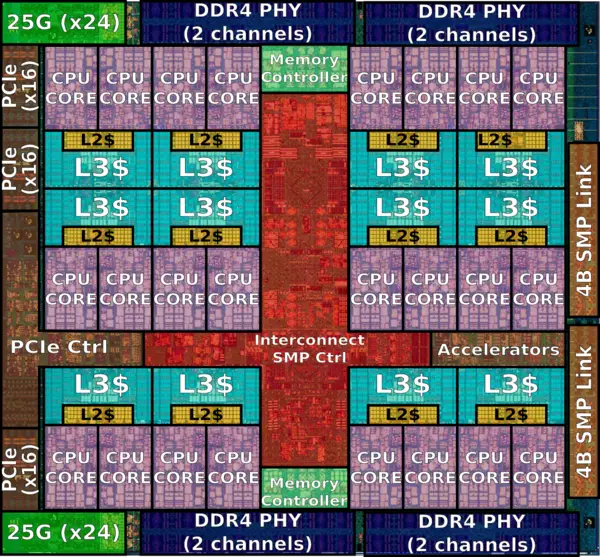

As seen here in this orientation (rotated 90-degrees from picture above):

The DIMM interfaces on the processor die are split half-top and half-bottom; the individual memory controllers are grouped on their respective edge and must run the same (maybe slowest plugged DIMM?) clock rate. I -think- top group vs. bottom group are independent enough to run different sizes and even speeds.

It is also very dependent on the firmware + software. Unclear to me if that will properly set up & use what the hardware sees.